|

| OwenDuffy.net |

|

This article describes an application of PllLdr to an AD9850 DDS.

The target DDS module was purchased on eBay for about A$12 including post. The module contains the AD9850 DDS chip, a 125MHz crystal reference, and low pass filter for the DDS output.

|

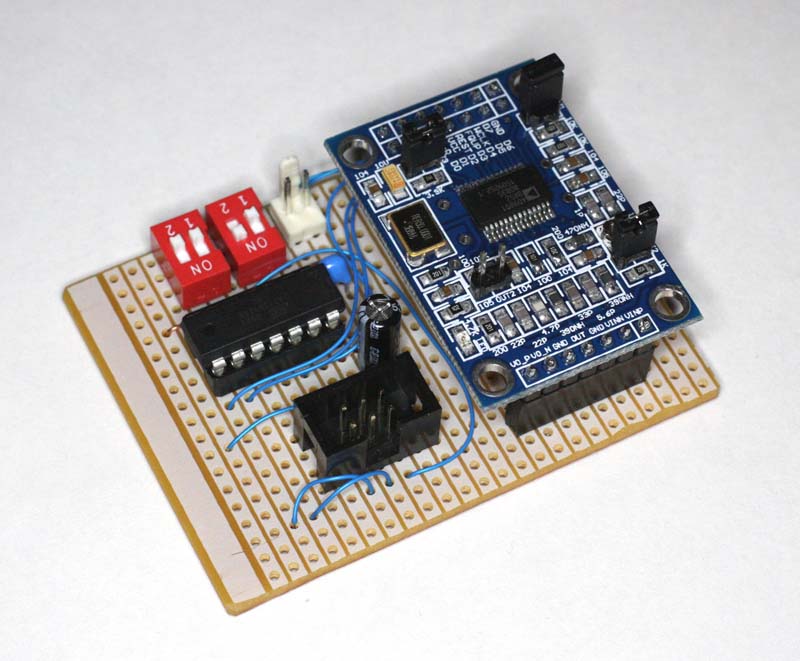

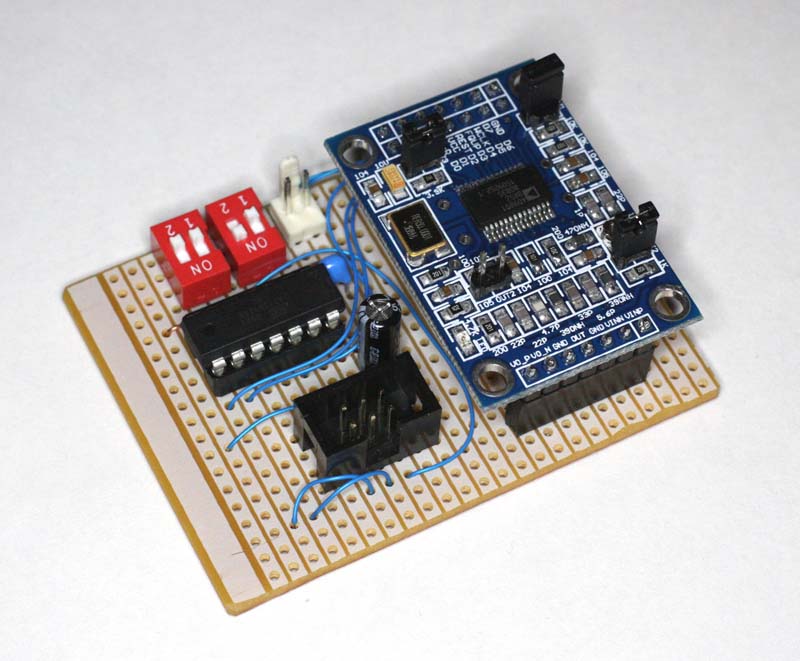

Fig 1 shows the prototype module. The DDS module which is fitted with header pins was accommodated on a small piece of Veroboard with a PllLdr hosted on an ATtiny24A, some DIP switches for selection of 1 of 16 frequencies from the channel memory in PllLdr EEPROM and an ISP socket.

Note that there is no adjustment of the frequency of the 125MHz crystal, so the factor loaded into the AD9850 must be adjusted to compensate for crystal error. In my case the crystal was 4kHz low (at 125MHz) so 32ppm must be added to the factor loaded into the AD9850. Short term stability is reasonable for a non-ovened crystal, on random observations over a day the frequency was within 100Hz at 7Mhz with an un-aged crystal.

{

"ver":"01","rbo":"R",

"options":"0100",

"regs":[["000E568CEB"],["000E568D96"]]

}

|

Above is an example EEPROM configuration file for a QRSS transmitter on 7.000800MHz with 5Hz FSK. QRSS keying is applied to pin 2 of the chip. Note that the factors used include calibration adjustments for this particular crystal.

The complete module is a synthesised oscillator good to 20 to 30MHz depending on waveform quality, frequency selectable from a bank of 16 frequencies stored in EEPROM.

Current consumption on 5V supply is about 100mA, and is less at 3.3V. Current consumption is lower also with a lower frequency reference, so if the operating requirement is for say lower HF, low voltage and a lower frequency crystal would reduce current consumption markedly.

For a few dollars more, AD9851 modules are available on eBay and they are good for up to about 70MHz.

(The procedure for switching the AD9850 to serial mode isn't straightforward SPI, but effectively it can be achieved at power up by sending the register data in serial mode twice, or to send power down code (04) at the start of each register set.)

| Version | Date | Description |

| 1.01 | 28/12/2011 | Initial. |

| 1.02 | ||

| 1.03 | ||

| 1.04 | ||

| 1.05 |

© Copyright: Owen Duffy 1995, 2021. All rights reserved. Disclaimer.